Apple a de nouveau surpris les passionnés et les analystes avec son annonce du M1 Ultra, une variante du M1 Max qui fusionne efficacement deux jetons en un.Le résultat est une conception à double puce considérée par le logiciel comme une seule pièce de silicium.NVIDIA a fourni des nouvelles similaires à la GPU Technology Conference 2022, où le PDG Jensen Huang a annoncé que la société fusionnera deux des nouveaux processeurs CPU Grace de la société en un seul "Superchip."

Ces annonces ciblent différents marchés.Apple a ses vues sur le monde des centres de travail des consommateurs et professionnels, tandis que Nvidia a l'intention de rivaliser dans l'informatique haute performance.Pourtant, la divergence dans l'objectif ne fait que souligner les grands défis qui mettent rapidement l'ère de la conception des puces monolithiques.

Le design MultiHip n'est pas nouveau, mais l'idée a augmenté en popularité au cours des cinq dernières années.AMD, Apple, Intel et Nvidia ont tous atténué à des degrés divers.AMD a poursuivi le design Chiplet avec ses processeurs EPYC et Ryzen.Intel prévoit de suivre le costume avec Sapphire Rapids, une architecture à venir pour le marché des serveurs construite sur l'utilisation de Chiplets qu'il appelle «Tiles." Now Apple and Nvidia have joined the party—though with designs that target significantly different markets.

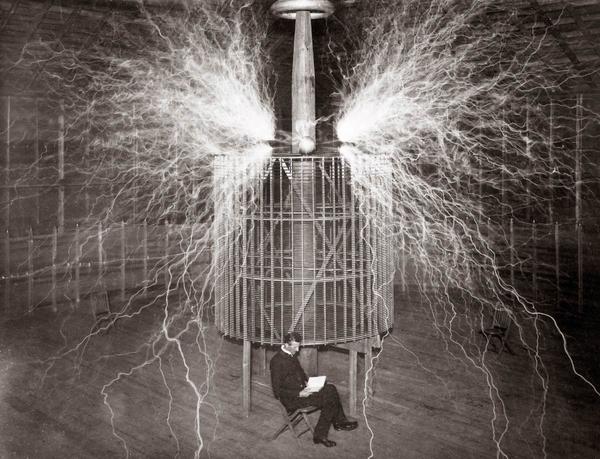

Nvidia’s Grace CPU SuperchipNvidia

Le passage vers la conception multi-chiens est motivé par le défi de la fabrication de puces modernes.La miniaturisation des transistors a ralenti, mais la croissance du nombre de transistors dans les conceptions de pointe ne montre aucun signe de ralentissement.

Apple’s M1 Ultra has 114 billion transistors and a die area (or fabrication area) of roughly 860 square millimeters (an official figure for the M1 Ultra is unavailable, but a single M1 Max chip has a die area of 432 mm2).Le nombre de transistors du CPU Grace de Nvidia est toujours sous les wraps, mais le GPU Hopper H100 annoncé aux côtés du CPU Grace comprend 80 milliards de transistors.Pour la perspective, le processeur EYPC Rome de 64 cœurs d'AMD, publié en 2019, en a 39.5 milliards de transistors.

Le transistor compte cette production de puces modernes à forte poussée à ses extrêmes, ce qui rend la conception Multichip plus attrayante. “Multichip module packaging has enabled the chip players to give better power efficiency and performance [with regard] to monolithic designs, as the die size for chips becomes larger and wafer-yield issues become more prominent," Akshara Bassi, a research analyst at Counterpoint Research, said in an email.Mis à part les Cerebras, une startup tentant de construire des puces qui s'étendent sur l'intégralité d'une tranche de silicium, l'industrie des puces semble en accord que la conception monolithique devient plus difficile qu'elle ne vaut.

Ce changement vers Chiplets s'est produit en étape avec le soutien des fabricants.Taiwan Semiconductor Manufacturing Co.est un leader, offrant une suite d'emballages avancés appelés 3DFabric.Les technologies qui relèvent de l'égide de 3DFABRIC sont utilisées par AMD dans certains conceptions de processeurs EPYC et Ryzen et sont presque certainement utilisées par Apple pour M1 Ultra (Apple n'a pas confirmé cela, mais le M1 Ultra est produit par TSMC).Intel a ses propres technologies d'emballage, comme EMIB et Foveros.Bien que destiné à l'origine à l'usage d'Intel, la technologie de fabrication de puces de la société devient pertinente pour l'industrie plus large, car les services Intel Foundry ouvrent ses portes.

“The ecosystem around the foundational semiconductor design, manufacturing, and packaging has progressed to the point of supporting the design nodes to economically and reliably produce chiplet-based solutions," Mark Nossokoff, a senior analyst at Hyperion Research, said in an email.«Les outils de conception de logiciels pour intégrer de manière transparente les diverses fonctionnalités de Chiplets ont également mûri pour optimiser les performances de la solution ciblée."

Les chiplets sont là pour rester, mais pour le moment, c'est un monde de silos.AMD, Apple, Intel et Nvidia utilisent leurs propres conceptions d'interconnexion destinées aux technologies d'emballage spécifiques.

Universal Chiplet Interconnection exprime les espoirs de rassembler l'industrie. Announced on 2 March 2022, this open standard offers a “standard" 2D package that targets “cost-effective performance" and an “advanced" package that targets leading-edge designs.UCie prend également en charge la connexion hors package via PCIE et CXL, ouvrant le potentiel de connexion de plusieurs puces sur plusieurs machines dans un environnement de calcul haute performance.

Un exemple d'options d'emballage UCIE du livre blanc UCie.Universal Chiplet Interconnection Express

Ucie est un début, mais l'avenir de la norme reste à voir. “The founding members of initial UCIe promoters represent an impressive list of contributors across a broad range of technology design and manufacturing areas, including the HPC ecosystem," said Nossokoff, “but a number of major organizations have not as yet joined, including Apple, AWS, Broadcom, IBM, NVIDIA, other silicon foundries, and memory vendors."

Bassi souligne que Nvidia peut être particulièrement réticent à participer.La société a ouvert sa propre interconnexion NVINK-C2C pour l'intégration de silicium personnalisée, ce qui en fait un concurrent potentiel pour UCIE.

Mais alors que le sort des interconnexions comme Ucie et Nvlink-C2C déterminera les règles du jeu, il est peu probable qu'ils changent le jeu en cours.Le M1 Ultra d'Apple pourrait être considéré comme le canari de la mine de charbon.La conception MultiHIP n'est plus réservée aux centres de données - il vient à un ordinateur à domicile près de chez vous.

From Your Site ArticlesRelated Articles Around the Web