Le PDG d'Intel, Pat Gelsinger, a annoncé son intention de récupérer la couronne de fabrication de copeaux de l'entreprise d'ici 2025.Mais l'entreprise a partagé plus de détails sur la recherche qui pourrait l'aider à concurrencer encore plus à l'avenir.

La société basée à Santa Clara, en Californie, a révélé un large éventail de nouvelles technologies dans son pipeline qui pourraient l'empêcher de prendre plus de retard sur la loi de Moore, ouvrant la porte à des processeurs plus petits, plus rapides et moins chers avec une meilleure efficacité.Au lieu de mettre à l'échelle physiquement les transistors au cœur de ses puces informatiques, Intel a proposé un moyen d'empiler les transistors eux-mêmes pour emballer en ressources informatiques plus.

Des chercheurs d'Intel ont décrit le travail dans les articles de la conférence IEDM à San Francisco, en Californie,.

La division de recherche principale d'Intel, le groupe de recherche des composants, est responsable de la création des technologies de processus et de réapprovisionnement qui l'aident à repousser les limites de la loi de Moore.La division de recherche maintient le pipeline de recherche et de développement d'Intel en collaboration avec ses unités commerciales pour anticiper les besoins futurs et en partenariat avec u.S.laboratoires de recherche, universités et autres fournisseurs de puces, entre autres groupes.

La division de recherche des composants occupe un rôle central dans les ambitions d'Intel de reprendre son leadership dans le déploiement des puces les plus avancées, une avance qu'il a cédé ces dernières années à des concurrents tels que TSMC.

Ruban

Intel essaie de riposter contre les concurrents en réorganisant l'architecture de ses transistors. Intel has previously said it plans to upgrade to "gate-all-around"—also known as "nanosheet"—transistors called Ruban in its 20A technology node.

Intel a annoncé son intention de commencer à fabriquer des puces avec de nouveaux transistors RibbonFet à l'intérieur d'ici 2024. The Ruban are based on sheets of current-carrying silicon stacked in a column. Unlike the FinFETs used in the most advanced chips on the market, where the gate is wrapped around a fin-shaped channel on three sides, the ribbon-shaped channels in Intel's Ruban are completely surrounded by the gate.

La forme tridimensionnelle du rubanfet signifie que plus de courant circulent pendant l'état "ON" et moins de courant pour fuir le canal lorsque le transistor est éteint "."La société a déclaré que cela se traduit par un meilleur contrôle électrostatique du transistor et moins de fuite de puissance, qui peut saper l'efficacité électrique du processeur final. In the end, the Ruban can consume lesspower and run faster and more efficiently.

Une autre technologie clé dans ThePipeline est un système de livraison de puissance arrière pour les transistors appelée Powervia.

Transistors CMOS 3D

À l'IEDM 2021, Intel a proposé une nouvelle technologie de processus où il empile les transistors nanochères les uns sur les autres pour créer plus d'espace sur la puce pour serrer les composants.Intel a déclaré que les transistors CMOS 3D lui permettraient d'emballer 30% jusqu'à 50% de transistors en plus dans chaque millimètre carré de silicium dans ses produits.

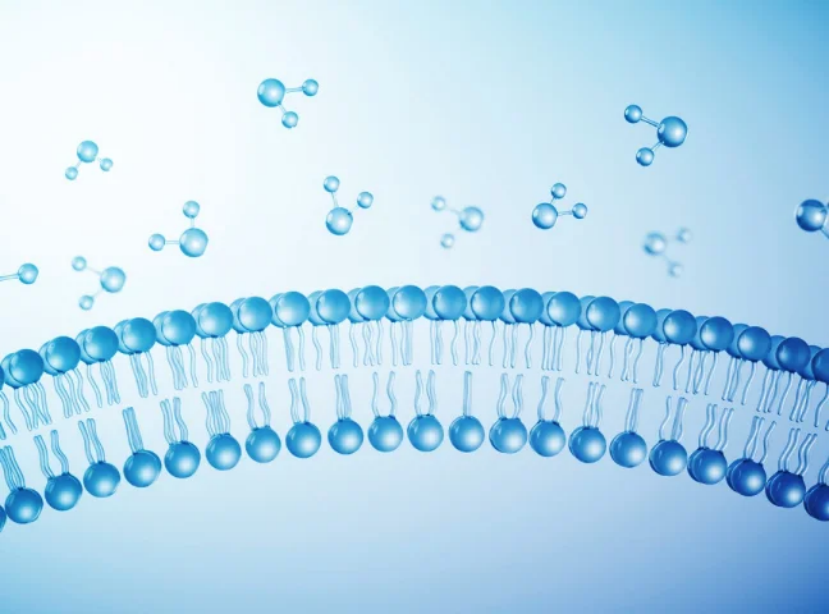

Les processeurs modernes les plus avancés contiennent des dizaines de milliards de transistors assemblés en portes logiques, qui sont à leur tour organisées en composants tels que les processeurs centraux et les caches de mémoire.Ces portes logiques sont basées sur des milliards de paires de transistors NMOS et PMOS.Les MOSFET sont étendus côte à côte sur le plan de la puce, avec un courant électrique traversant les interconnexions entre elles.

Mais empiler les transistors entraîne une métropole en silicium avec tout ce qui est plus proche les uns des autres.Cela réduirait également la distance que le courant doit parcourir le transistor au transistor, augmentant l'efficacité énergétique.

Il pourrait prendre des années à Intel pour améliorer les transistors CMOS 3D au point où il serait logique de commencer la production de masse.Mais la technologie de transistor 3D pourrait donner à Intel un autre levier à tirer pour améliorer la vitesse et l'efficacité de ses puces.

"Chez Intel, la recherche et l'innovation nécessaires pour faire progresser la loi de Moore ne s'arrête jamais", a déclaré Robert Chau, directeur général du bras de recherche des composantes d'Intel, dans un communiqué.

Emballage 3D

Intel investit également dans son arsenal d'emballage avancé pour emballer plus de puissance de calcul dans la même zone de silicium.Le géant semi-conducteur prévoit de commencer à déployer plus de produits en empilant de minuscules dalles de silicium appelées "Chiplets ou" tuiles "les unes sur les autres en trois dimensions, en mélangeant et en faisant correspondre une large gamme de tuiles au lieu de tout charger sur un seul système sur un seul système sur un systèmepuce (SOC).

Intel utilise sa technologie d'emballage 3D appelée Foveros pour empiler les carreaux avec une liaison directe de cuivre à cuivre des interconnexions de relais des données entre les tuiles.Cela se traduit par une meilleure efficacité énergétique, une densité d'interconnexion et un routage du signal, tout en limitant la dissipation de la chaleur.Intel a déclaré qu'il pouvait profiter de Foveros pour placer les interconnexions sur le dessous d'un dé.

Intel a déclaré que son service de recherche travaille maintenant sur la prochaine génération appelée Foveros Direct qui réduit l'écart entre les interconnexions à moins de 10 µm.

La société a déclaré qu'elle visait une augmentation de plus de dix de la densité d'interconnexion avec Foveros Direct.Cela pourrait réduire le temps nécessaire aux données pour voyager entre les carreaux dans un package, augmentant les performances.

Intel a déclaré que ses composants recherchent Armis travaillant sur un large éventail de nouvelles technologies en parallèle, liées aux transistors, à l'emballage, à la mémoire et aux interconnexions ainsi qu'à l'informatique quantique et à de nouveaux matériaux.Intel a déclaré qu'il recherchait également des commutateurs GAN pour une puissance de puce plus efficace.